# Comparative Analysis of GDI and CMOS Logic for Low Power VLSI Design: A Case Study on 4-bit Hamming Code Encoder and Decoder

Mr.K.Srikanth a, T.Ganesh b, G.Ashrithac, K.Rohith d, G.Ganeshe, Musheer Ahmed Khanf

#### Abstract:

This Paper presents an in-depth analysis of Gate Diffusion Input (GDI) and Complementary Metal-Oxide-Semiconductor (CMOS) logic types in the context of designing a 4-bit Hamming code encoder and decoder. The Project focuses on simulations conducted using Gpdk 250 nm technology to evaluate power consumption, latency, and transistor count. The results demonstrate that GDI logic offers significant advantages over CMOS logic, including nearly 50% power savings, reduced latency, and fewer transistors. These findings highlight the potential of GDI logic as a superior low power design choice for VLSI circuit designers.

Keywords: PMOS, NMOS, VLSI, CMOS, GDI, Hamming code, Encoder, Decoder 1. Introduction:

The goal of error-free data communication in digital systems has led to the development of robust error detection and repair algorithms. What sets Hamming codes apart from the rest is their ability to detect and correct single-bit errors in transmitted data. When combined with Gate Diffusion Input (GDI) logic, Hamming codes offer a dependable and efficient way to ensure data integrity in communication systems.

GDI logic, being well-known for its compactness and energy efficiency, enables the design of encoders and decoders for the Hamming code. By applying the ideas of GDI logic, designers can create compact, power-efficient circuits that encode and decode data and have integrated error detection and repair.

This brief introduction looks at the connection between Hamming codes and GDI logic and demonstrates how GDI-based designs can increase the reliability and efficiency of data communication systems. By integrating GDI logic, hamming code encoders and decoders can offer robust error detection and correcting procedures, enabling error-free data transport in a range of digital communication applications.

#### 2. GATE DIFFUSION INPUT (GDI) TECHNIQUE

<sup>&</sup>lt;sup>a</sup> Assistant Professor, Dept. Of ECE Balaji Institute of Technology and Science Narsampet Warangal.

<sup>&</sup>lt;sup>b</sup> Student, Dept. Of ECE Balaji Institute of Technology and Science Narsampet Warangal.

<sup>&</sup>lt;sup>c</sup> Student, Dept. Of ECE Balaji Institute of Technology and Science Narsampet Warangal.

<sup>&</sup>lt;sup>d</sup> Student, Dept. Of ECE Balaji Institute of Technology and Science Narsampet Warangal.

<sup>&</sup>lt;sup>e</sup> Student, Dept. Of ECE Balaji Institute of Technology and Science Narsampet Warangal.

<sup>&</sup>lt;sup>f</sup> Student, Dept. Of ECE Balaji Institute of Technology and Science Narsampet Warangal.

Gate Diffusion Input (GDI) is a digital logic style that is used to implement Boolean functions in integrated circuits. It is known for its simplicity, reduced transistor count, and potential for low-power consumption.

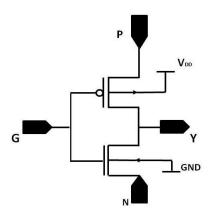

The GDI (Gate Diffusion Input) logic cell, which has four terminals—Inputs G, P, and N—as well as an output (Y), is shown in Figure 1. The N-MOS and P-MOS transistors share a same gate in the gate input (G). Similar to the VDD connection in a typical CMOS inverter, the input P is connected to the source of the P-MOS transistor. Like the ground connection in a CMOS inverter, the input N of the N-MOS transistor is connected to its source. The transistors' common drain terminal is where the output Y is obtained.

Figure 1: Basic GDI cell

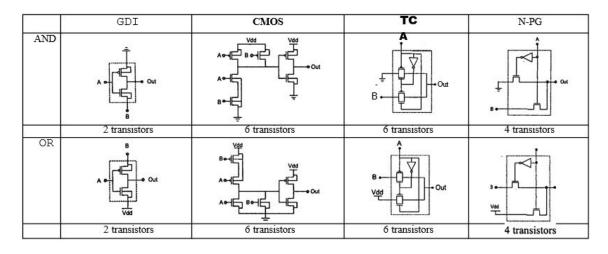

Table1: GDI, CMOS, and PTL design methodologies used to AND and OR cells.

Table2: Different GDI Cell-Based Logic Functions and Their Input Combinations

| l F          | Basic | funct   | No. of transistors |                         |     |      |  |

|--------------|-------|---------|--------------------|-------------------------|-----|------|--|

| $\mathbf{G}$ | P     | N       | FUNC               | <b>OUTPUT</b>           | GDI | CMOS |  |

| A            | В     | 1       | OR                 | A+B                     | 2   | 6    |  |

| A            | 0     | В       | AND                | A.B                     | 2   | 6    |  |

| Α            | В     | С       | MUX                | $\bar{A}.B + A.C$       | 2   | 12   |  |

| Α            | В     | $ar{A}$ | XOR                | $\bar{A}.B + A.\bar{B}$ | 4   | 16   |  |

| Α            | 1     | 0       | INV                | $ar{A}$                 | 2   | 2    |  |

ResMilitaris, vol.14 n°,4 ISSN: 2265-6294 (2024)

#### 3. Generation of Hamming Code

The Hamming code is a method for generating error-correcting codes that can detect and correct single-bit errors in transmitted data. Here is a concise explanation of how to generate Hamming code:

#### The key steps are:

- i. Compute the required number of redundant/parity bits (r) and data bits (m). It is related as follows:  $2^r \ge m + r + 1$ . For instance, r = 4 redundant bits are required if there are 7 data bits.

- ii. Empty the parity bit locations and allocate the data bits to certain codeword locations. The positions of the parity bits are powers of two, such as 1, 2, 4, 8, etc.

- iii. Determine the parity bit positions and then compute the parity bits by comparing the parities of the bits in the respective patterns:

- iv. Parity bit 1 verifies that bits at places 1, 3, 5, 7, and so on are in parity.

- v. Parity bit 2 verifies the bits at places 2, 3, 6, 7, and so on are in parity.

- vi. Parity bit 4 verifies the bits in places 4–7, 12–15, and so on are in parity.

- vii. For the remaining parity bits, continue as before.

- viii. To make the parity of the checked bits even, set each parity bit to 0 or 1.

- ix. Because the generated codeword includes both the calculated parity bits and the original data bits, single-bit errors can be found and fixed.

**Table 3**: Shows the Formation of Hamming Code

| Hamming code bit position | $H_1$ | $H_2$ | $H_3$ | $H_4$ | $H_5$ | $H_6$ | $H_7$ |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|

| Type of data bit          | $P_1$ | $P_2$ | $D_1$ | $P_3$ | $D_2$ | $D_3$ | $D_4$ |

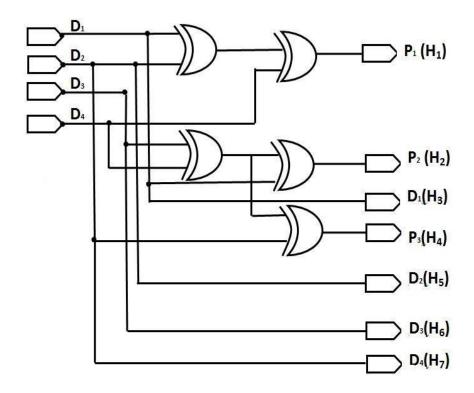

#### 3.1 Hamming code Encoder

XOR gates can be used to implement the architecture of the Hamming code encoder (either for even parity or odd parity). The construction of the Hamming code encoder is shown in the Figure 2.

Figure 2: Hamming Code Encoder

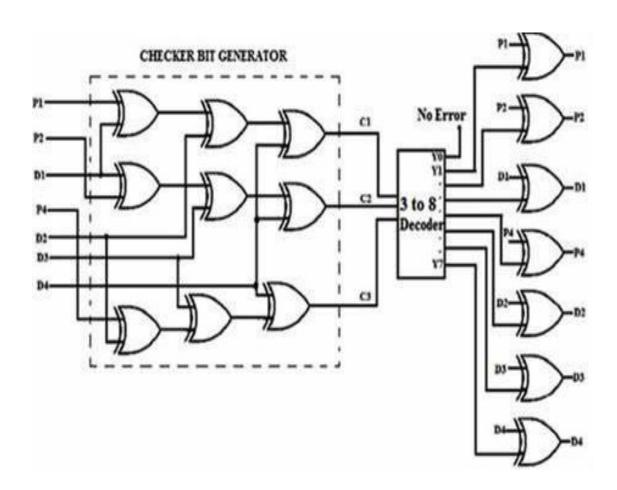

#### 3.2 Hamming Code Decoder

A Hamming code decoder is used at the receiving end of digital data transfer to decode data packets and fix any errors. The code word produced by the encoder circuit is conveyed through the transmission media during data transmission. When the decoder receives the code word, it looks for mistakes.

There are two steps in the decoding process. Using a check bit generator that functions similarly to the encoder, the decoder first creates check bits to confirm the parity of the data it has received. In the second phase, the decoder uses a 3-to-8 decoder to locate the error bit locations and de-multiplexers to fix them if the check bit generator finds any mistakes. The Hamming code decoder's architecture is depicted in Figure 3.

Figure 3: Hamming Code Decoder

#### 4. Simulation Results:

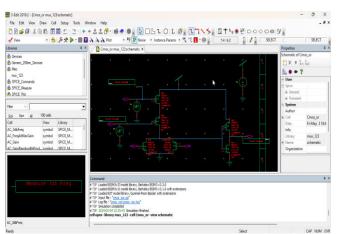

#### 4.1 Design and Simulation Results of CMOS OR Gate

Figure 4: Design of CMOS OR Gate

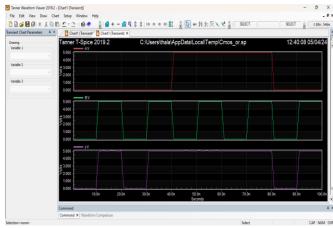

Figure 5: Output waveforms of CMOS OR Gate

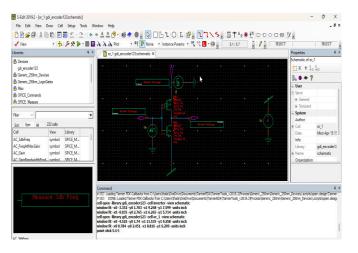

#### 4.2 Design and Simulation Results of GDI OR Gate

Figure 6: Design of GDI OR Gate

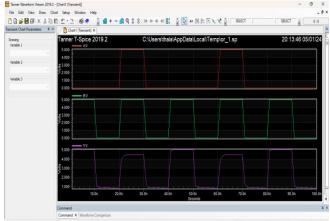

Figure 7: Output Waveforms of OR Gate

Table 4: Message Bits Transmission at Encoder Side

| Hamming code bit                | H1 | H2 | Н3 | Н4 | Н5 | Н6 | Н7 |

|---------------------------------|----|----|----|----|----|----|----|

| position<br>Type of data<br>bit | P1 | P2 | D1 | Р3 | D2 | D3 | D4 |

| Message bits for transmission   | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

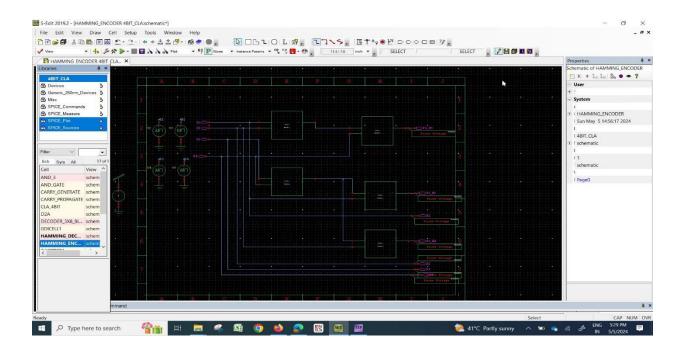

#### 4.3 Design and Simulation Results of GDI Encoder

Figure 8: Hamming Code Encoder using GDI logic

Figure 9: Hamming Code Encoder output waveforms

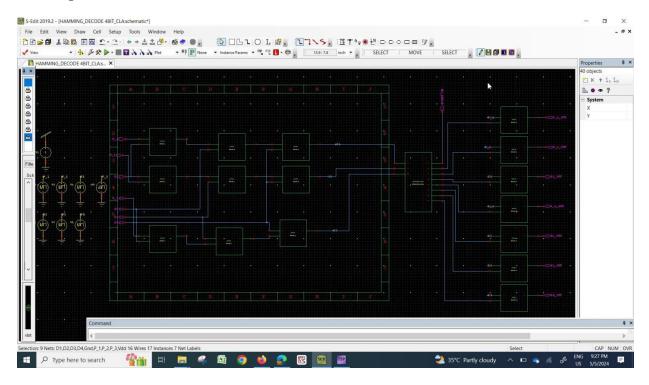

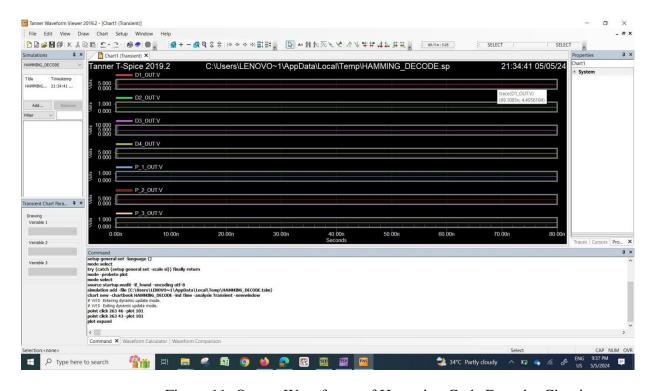

#### 4.4 Design and Simulation Results of GDI Decoder

Figure 10: Design of Hamming Code Decoder circuit

Figure 11: Output Waveforms of Hamming Code Decoder Circuit

**Table 4**: Message Bits Transmission at Encoder Side with Single bit error and Received data at Decode side without error.

| Hamming code bit                                                        | H1 | Н2 | Н3 | Н4 | Н5 | Н6 | Н7 |

|-------------------------------------------------------------------------|----|----|----|----|----|----|----|

| position<br>Type of data<br>bit                                         | P1 | P2 | D1 | Р3 | D2 | D3 | D4 |

| Message bits for transmission                                           | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| Message bits<br>for<br>transmission<br>with Error<br>at Encoder<br>Side | 0  | 1  | 1  | 0  | 0  | 1  | 0  |

| Original message Received at Decoder Side without Error                 | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

#### 5. Conclusion:

In this study, we explored various GDI (Gate Diffusion Input) logic functions designed for low-power VLSI architecture and conducted simulations to compare them with traditional CMOS logic. We specifically focused on designing and simulating a 4-bit Hamming code encoder and decoder using both GDI and CMOS logic types, utilizing Gpdk 250 nm technology for our experiments. The simulation results revealed that GDI logic provides significant advantages over CMOS logic. Notably, GDI achieved nearly 50% power savings compared to CMOS. Moreover, GDI showed a marked improvement in latency and required fewer transistors for performing operations. By simulating Hamming encoder and decoder circuits with both GDI and CMOS logic, we were able to thoroughly evaluate the benefits of the GDI approach. Overall, our findings clearly indicate that GDI logic is a superior choice for VLSI circuit designers seeking low-power design solutions.

#### 6. Future Work:

There are a number of intriguing directions for future development in GDI Logic Based Design of Hamming-Code Encoder and Decoder for Error-Free Data Communication. To obtain higher degrees of error detection and repair, researchers should first investigate more complex error correction codes, such as Reed-Solomon or Turbo codes, which go beyond Hamming codes. Moreover, investigating hardware implementations on FPGA or ASIC platforms would make real-time, error-free data transfer applications possible. Throughput and efficiency might be increased by experimenting with techniques like parallel processing, and in areas where energy is limited, it is critical to optimize designs for low power consumption. Fortifying data integrity and including security measures can strengthen it

## RES MILITARIS

## **Social Science Journal**

against malevolent assaults and improve fault tolerance. Practical effectiveness requires interdisciplinary collaboration for cross-layer optimization and design validation in real-world deployments. Lastly, dynamically modifying encoding and decoding algorithms in response to channel conditions and data patterns might be achieved by using machine learning approaches for adaptive error correction. Together, these approaches seek to further the frontiers of error-free data transfer by utilizing Hamming codes and GDI logic design concepts for improved dependability and performance.

#### **References:**

- [1] P. Chandrakasan and R. W. Brodersen, "Minimizing power consumption in digital CMOS circuits," in Proceedings of the IEEE, vol. 83, no. 4, pp. 498-523, April 1995.

- [2] W. Al-Assadi, A.P. Jayasumana and Y.K.Malaiya, Pass Transistor Logic Design, International Journal of Electronics, 1991,vol.70, no.4, pp. 739-749.

- [3] I.S. Abu-Khater, A.Bellaour, M.I. Elmastry, Circuit Techniques for CMOS Low-Power High-Performance Multipliers, IEEE Journal of Solid-State Circuits, vol.31, no.10, pp. 1535-1546, October 1996.

- [4] ArkadiyMorgenshtein, Alexander Fish, Israel A.Wagner Gate Diffusion Input(GDI) A Technique for Low Power Design of Digital Circuits: Analysis and Characterization IEEE 2002, pp. 477-480.

- [5] A.P. Chandrakasan, S. Sheng and R. W. Brodersen, Low-Power CMOS Digital Design ,IEEE Journal of Solid-State Circuits, vol.27 ,pp. 473- 484, April 1992.

- [6] Sanjay Sharma, Digital communication ,SK Kataria and Sons Publication 2007.

- [7] Madhu Kumar Vanteru, K.A. Jayabalaji, i-Sensor Based healthcare monitoring system by LoWPAN-based rchitecture, Measurement: Sensors, Volume 28,2023,100826, ISSN 2665-9174, https://doi.org/10.1016/j.measen.2023.100826.

- [8] Ramesh, P.S., Vanteru, Madhu.Kumar., Rajinikanth, E. *et al.* Design and Optimization of Feedback Controllers for Motion Control in the Manufacturing System for Digital Twin. *SN COMPUT. SCI.* **4**, 782 (2023). https://doi.org/10.1007/s42979-023-02228-8

- [9] Madhu. Kumar. Vanteru, T. V. Ramana, *et al*, "Modeling and Simulation of propagation models for selected LTE propagation scenarios," 2022 International Conference on Recent Trends in Microelectronics, Automation, Computing and Communications Systems (ICMACC), Hyderabad, India, 2022, pp. 482-488, doi: 10.1109/ICMACC54824.2022.10093514.

- [10] Allanki Sanyasi Rao, **Madhu Kumar Vanteru** et al. (2023). PAPR and BER Analysis in FBMC/OQAM System with Pulse Shaping Filters and Various PAPR Minimization Methods. *International Journal on Recent and Innovation Trends in Computing and Communication*, 11(10), 2146–2155. https://doi.org/10.17762/ijritcc.v11i10.8899.

- [11] N. Sivapriya, Madhu Kumar Vanteru, et al, "Evaluation of PAPR, PSD, Spectral Efficiency, BER and SNR Performance of Multi-Carrier Modulation Schemes for 5G and Beyond," *SSRG International Journal of Electrical and Electronics Engineering*, vol. 10, no. 11, pp. 100-114, 2023. *Crossref*, https://doi.org/10.14445/23488379/IJEEE-V10I11P110

- [12] Chandini Banapuram, Azmera Chandu Naik, Madhu Kumar Vanteru, et al, "A Comprehensive Survey of Machine Learning in Healthcare: Predicting Heart and Liver Disease, Tuberculosis Detection in Chest X-Ray Images," *SSRG International Journal of Electronics and Communication Engineering*, vol. 11, no. 5, pp. 155-169, 2024. *Crossref*, https://doi.org/10.14445/23488549/IJECE-V1115P116.

- [13] Madhu. Kumar. Vanteru, et al, "Empirical Investigation on Smart Wireless Autonomous Robot for Landmine Detection with Wireless Camera," 2022 5th International Conference on Contemporary Computing and Informatics (IC3I), Uttar Pradesh, India, 2022, pp. 200-205, doi: 10.1109/IC3I56241.2022.10072936.

- [14] S. Bhatnagar, Madhu. Kumar. Vanteru et al., "Efficient Logistics Solutions for E-Commerce Using Wireless Sensor Networks," in IEEE Transactions on Consumer Electronics, doi: 10.1109/TCE.2024.3375748.

- [15] V, Sravan Kumar, Madhu Kumar Vanteru et al. 2024. "BCSDNCC: A Secure Blockchain SDN Framework for IoT and Cloud Computing". *International Research Journal of Multidisciplinary Technovation* 6 (3):26-44. https://doi.org/10.54392/irjmt2433.

- [16] Madhu Kumar, Vanteru. & Ramana, T.. (2022). Fully scheduled decomposition channel estimation based MIMO-POMA structured LTE. International Journal of Communication Systems. 35. 10.1002/dac.4263.

- [17] Vanteru. Madhu. Kumar and T. V. Ramana, "Position-based Fully-Scheduled Precoder Channel Strategy for POMA Structured LTE Network," 2019 IEEE International Conference on Electrical, Computer and Communication Technologies (ICECCT), Coimbatore, India, 2019, pp. 1-8, doi: 10.1109/ICECCT.2019.8869133.

- [18] Madhu. Kumar. Vanteru, T. V. Ramana, A. C. Naik, C. Adupa, A. Battula and D. Prasad, "Modeling and Simulation of propagation models for selected LTE propagation scenarios," 2022 International Conference on Recent Trends in Microelectronics, Automation, Computing and Communications Systems (ICMACC), Hyderabad, India, 2022, pp. 482-488, doi: 10.1109/ICMACC54824.2022.10093514.

- [19] Vanteru.Madhu Kumar,Dr.T.V.Ramana" Virtual Iterative Precoding Based LTE POMA Channel Estimation Technique in Dynamic Fading Environments" International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-8 Issue-6, April 2019

- [20] Vanteru .Madhu Kumar,Dr.T.V.Ramana, Rajidi Sahithi" User Content Delivery Service for Efficient POMA based LTE Channel Spectrum Scheduling Algorithm" International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-9 Issue-2S3, December 2019.

- [21] Vanteru.Madhu Kumar,Dr.T.V.Ramana" Virtual Iterative Precoding Based LTE POMA Channel Estimation Technique in Dynamic Fading Environments" International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-8 Issue-6, April 2019

- [22] Karthik Kumar Vaigandla and J. Benita, "PAPR REDUCTION OF FBMC-OQAM SIGNALS USING PHASE SEARCH PTS AND MODIFIED DISCRETE FOURIER TRANSFORM SPREADING," ARPN Journal of Engineering and Applied Sciences, VOL. 18, NO. 18, pp.2127-2139, SEPTEMBER 2023

- [23] aigandla, Karthik Kumar and Benita, J. 'Selective Mapping Scheme Based on Modified Forest Optimization Algorithm for PAPR Reduction in FBMC System'. Journal of Intelligent & Fuzzy Systems, vol. 45, no. 4, pp. 5367-5381, October 2023, DOI: 10.3233/JIFS-222090.

- [24] Vaigandla, K. K. ., & Benita, J. (2023). A Novel PAPR Reduction in Filter Bank Multi-Carrier (FBMC) with Offset Quadrature Amplitude Modulation (OQAM) Based VLC Systems. *International Journal on Recent and Innovation Trends in Computing and Communication*, 11(5), 288–299. https://doi.org/10.17762/ijritcc.v11i5.6616

- [25] Karthik Kumar Vaigandla, J.Benita, "PRNGN PAPR Reduction using Noise Validation and Genetic System on 5G Wireless Network," International Journal of Engineering Trends and Technology, vol. 70, no. 8, pp. 224-232, 2022. Crossref, https://doi.org/10.14445/22315381/IJETT-V70I8P223

- [26] Karthik Kumar Vaigandla and J.Benita (2022), Novel Algorithm for Nonlinear Distortion Reduction Based on Clipping and Compressive Sensing in OFDM/OQAM System. IJEER 10(3), 620-626. https://doi.org/10.37391/IJEER.100334.

- [27] K. K. Vaigandla, "Communication Technologies and Challenges on 6G Networks for the Internet: Internet of Things (IoT) Based Analysis," 2022 2nd International Conference on Innovative Practices in Technology and Management (ICIPTM), 2022, pp. 27-31, doi: 10.1109/ICIPTM54933.2022.9753990.

- [28] Vaigandla, K. K., Karne, R., Siluveru, M., & Kesoju, M. (2023). Review on Blockchain Technology: Architecture, Characteristics, Benefits, Algorithms, Challenges and Applications. *Mesopotamian Journal of CyberSecurity*, 2023, 73–85. https://doi.org/10.58496/MJCS/2023/012

- [29] Karthik Kumar Vaigandla, Allanki Sanyasi Rao and Kallepelli Srikanth. Study of Modulation Schemes over a Multipath Fading Channels. International Journal for Modern Trends in Science and Technology 2021, 7 pp. 34-39. https://doi.org/10.46501/IJMTST0710005

- [30] Karthik Kumar Vaigandla, Bolla Sandhya Rani, Kallepelli Srikanth, Thippani Mounika, RadhaKrishna Karne, "Millimeter Wave Communications: Propagation Characteristics, Beamforming, Architecture, Standardization, Challenges and Applications". Design Engineering, Dec. 2021, pp. 10144-10169,

- [31] Karthik Kumar Vaigandla, Radhakrishna Karne, Allanki Sanyasi Rao, "Analysis of MIMO-OFDM: Effect of Mutual Coupling, Frequency Response, SNR and Channel Capacity", YMER Digital ISSN:0044-0477, vol.20, no.10 2021, pp.118-126, 2021.

- [32] Karthik Kumar Vaigandla, Shivakrishna Telu, Sandeep Manikyala, Bharath Kumar Polasa, Chelpuri Raju, "Smart And Safe Home Using Arduino," International Journal Of Innovative Research In Technology, Volume 8, Issue 7, 2021,pp.132-138

- [33] Karthik Kumar Vaigandla, Mounika Siluveru and Sandhya Rani Bolla, "Analysis of PAPR and Beamforming For 5G MIMO-OFDM", International journal of analytical and experimental modal analysis, Volume XII, Issue X, 2020, pp.483-490.

- [34] D. Priyanka, V. Karthik, "Wireless Surveillance Robot with Motion Detection and Live Video Transmission and Gas Detection," International Journal of Scientific Engineering and Technology Research, Vol.04, Issue. 17, June-2015, Pages: 3099-3106